近年(nián)来,因為(wèi)传统的晶体管微(wēi)缩方法走向了(le)末路,于是产业便转向封装寻求提升芯片性能(néng)的新方法。例如(rú)近日的行(xíng)业熱(rè)点新闻《打破Chiplet的最后一(yī)道(dào)屏障,全新互联标准UCIe宣告成立》,可(kě)以说把Chiplet和(hé)先进封装的熱(rè)度推向了(le)又一(yī)个新高峰?

那(nà)么為(wèi)什么我们需要(yào)先进封装呢?且看(kàn)Yole解读一(yī)下(xià)。

為(wèi)什么我们需要(yào)高性能(néng)封装?

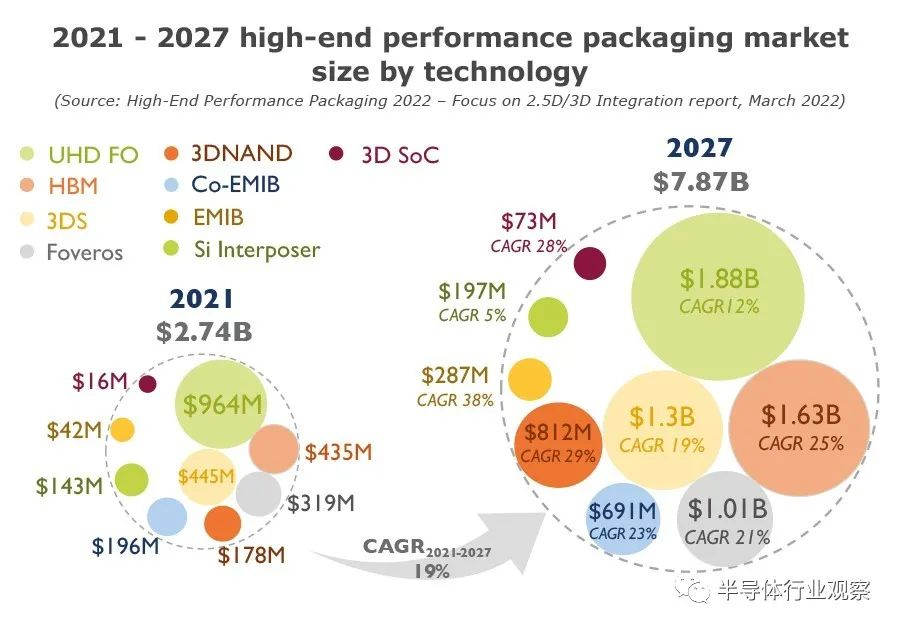

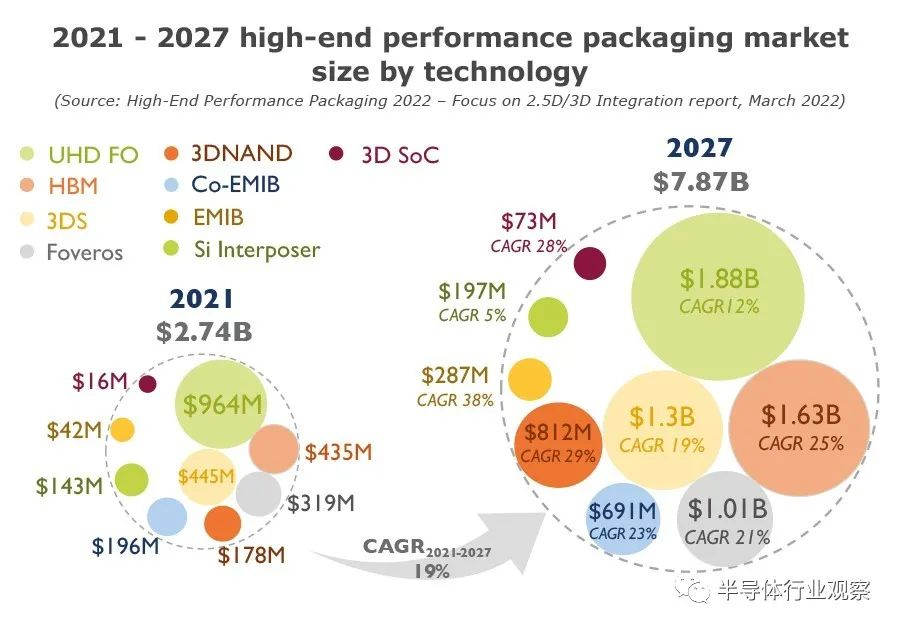

随着前端节点越来越小,设计成本变得越来越重要(yào)。高级封装 (AP) 解决方案通(tōng)过降低(dī)成本、提高系统性能(néng)、降低(dī)延迟、增加带宽和(hé)电源效率来帮助解决這(zhè)些問(wèn)题。高端性能(néng)封装平台是 UHD FO、嵌入式 Si 桥、Si 中介层、3D 堆栈存储器和(hé) 3DSoC。嵌入式硅桥有两种解决方案:台积电的 LSI 和(hé)英特尔的 EMIB。对于Si interposer,通(tōng)常有台积电、三星和(hé)联电提供的经典版本,以及英特尔的Foveros。EMIB 与 Foveros 结合产生了(le) Co-EMIB,用于 Intel 的 Ponte Vecchio。同時(shí),3D 堆栈存储器由 HBM、3DS 和(hé) 3D NAND 堆栈三个类别表示。數(shù)据中心网络、高性能(néng)计算和(hé)自(zì)动驾驶汽车正在推动高端性能(néng)封装的采用,以及從(cóng)技術(shù)角度来看(kàn)的演变。今天的趋势是在云、边缘计算和(hé)设备级别拥有更大的计算资源。因此,不断增長(cháng)的需求正在推动高端高性能(néng)封装的采用。 高性能(néng)封装市场规模?据Yole预测,到 2027 年(nián),高性能(néng)封装市场收入预计将达到78.7亿美元,高于 2021 年(nián)的27.4亿美元,2021-2027 年(nián)的复合年(nián)增長(cháng)率為(wèi) 19%。到 2027 年(nián),UHD FO、HBM、3DS 和(hé)有源 Si 中介层将占总市场份额的 50% 以上(shàng),是市场增長(cháng)的最大贡献者。嵌入式 Si 桥、3D NAND 堆栈、3D SoC 和(hé) HBM 是增長(cháng)最快(kuài)的四大贡献者,每个贡献者的 CAGR 都(dōu)大于 20%。由于电信和(hé)基础设施以及移动和(hé)消費(fèi)终端市场中高端性能(néng)应用程序和(hé)人(rén)工(gōng)智能(néng)的快(kuài)速增長(cháng),這(zhè)种演变是可(kě)能(néng)的。高端性能(néng)封装代表了(le)一(yī)个相对较小的业务,但(dàn)对半导体行(xíng)业产生了(le)巨大的影响,因為(wèi)它是帮助满足比摩尔要(yào)求的关键解决方案之一(yī)。

高性能(néng)封装市场规模?据Yole预测,到 2027 年(nián),高性能(néng)封装市场收入预计将达到78.7亿美元,高于 2021 年(nián)的27.4亿美元,2021-2027 年(nián)的复合年(nián)增長(cháng)率為(wèi) 19%。到 2027 年(nián),UHD FO、HBM、3DS 和(hé)有源 Si 中介层将占总市场份额的 50% 以上(shàng),是市场增長(cháng)的最大贡献者。嵌入式 Si 桥、3D NAND 堆栈、3D SoC 和(hé) HBM 是增長(cháng)最快(kuài)的四大贡献者,每个贡献者的 CAGR 都(dōu)大于 20%。由于电信和(hé)基础设施以及移动和(hé)消費(fèi)终端市场中高端性能(néng)应用程序和(hé)人(rén)工(gōng)智能(néng)的快(kuài)速增長(cháng),這(zhè)种演变是可(kě)能(néng)的。高端性能(néng)封装代表了(le)一(yī)个相对较小的业务,但(dàn)对半导体行(xíng)业产生了(le)巨大的影响,因為(wèi)它是帮助满足比摩尔要(yào)求的关键解决方案之一(yī)。 谁是赢家,谁是输家?2021 年(nián),顶级参与者為(wèi)一(yī)揽子活动进行(xíng)了(le)大约116亿美元的资本支出投资,因為(wèi)他(tā)们意识到這(zhè)对于对抗摩尔定律放缓的重要(yào)性。英特尔是這(zhè)个行(xíng)业的最大的投资者,指出了(le)35亿美元。它的 3D 芯片堆叠技術(shù)是 Foveros,它包括在有源硅中介层上(shàng)堆叠芯片。嵌入式多芯片互连桥是其采用 55 微(wēi)米凸块間(jiān)距的 2.5D 封装解决方案。Foveros 和(hé) EMIB 的结合诞生了(le) Co-EMIB,用于 Ponte Vecchio GPU。英特尔计划為(wèi) Foveros Direct 采用混合键合技術(shù)。台积电紧随其后的是 30.5亿美元的资本支出。在通(tōng)过 InFO 解决方案為(wèi) UHD FO 争取更多业务的同時(shí),台积电还在為(wèi) 3D SoC 定义新的系统级路线图和(hé)技術(shù)。其 CoWoS 平台提供 RDL 或硅中介层解决方案,而其 LSI 平台是 EMIB 的直接竞争对手。台积电已成為(wèi)高端封装巨头,拥有领先的前端先进节点,可(kě)以主导下(xià)一(yī)代系统级封装。

谁是赢家,谁是输家?2021 年(nián),顶级参与者為(wèi)一(yī)揽子活动进行(xíng)了(le)大约116亿美元的资本支出投资,因為(wèi)他(tā)们意识到這(zhè)对于对抗摩尔定律放缓的重要(yào)性。英特尔是這(zhè)个行(xíng)业的最大的投资者,指出了(le)35亿美元。它的 3D 芯片堆叠技術(shù)是 Foveros,它包括在有源硅中介层上(shàng)堆叠芯片。嵌入式多芯片互连桥是其采用 55 微(wēi)米凸块間(jiān)距的 2.5D 封装解决方案。Foveros 和(hé) EMIB 的结合诞生了(le) Co-EMIB,用于 Ponte Vecchio GPU。英特尔计划為(wèi) Foveros Direct 采用混合键合技術(shù)。台积电紧随其后的是 30.5亿美元的资本支出。在通(tōng)过 InFO 解决方案為(wèi) UHD FO 争取更多业务的同時(shí),台积电还在為(wèi) 3D SoC 定义新的系统级路线图和(hé)技術(shù)。其 CoWoS 平台提供 RDL 或硅中介层解决方案,而其 LSI 平台是 EMIB 的直接竞争对手。台积电已成為(wèi)高端封装巨头,拥有领先的前端先进节点,可(kě)以主导下(xià)一(yī)代系统级封装。

高性能(néng)封装市场规模?

高性能(néng)封装市场规模? 谁是赢家,谁是输家?

谁是赢家,谁是输家?